Figure 1 from Implementation of a Loosely-Coupled Lockstep Approach in the Xilinx Zynq-7000 All Programmable SoC for High Consequence Applications | Semantic Scholar

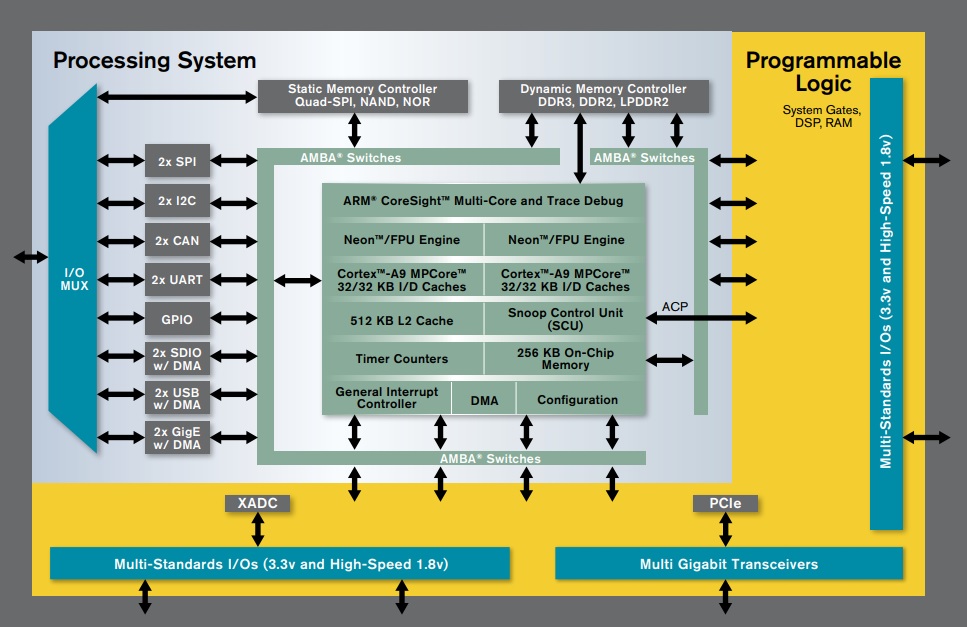

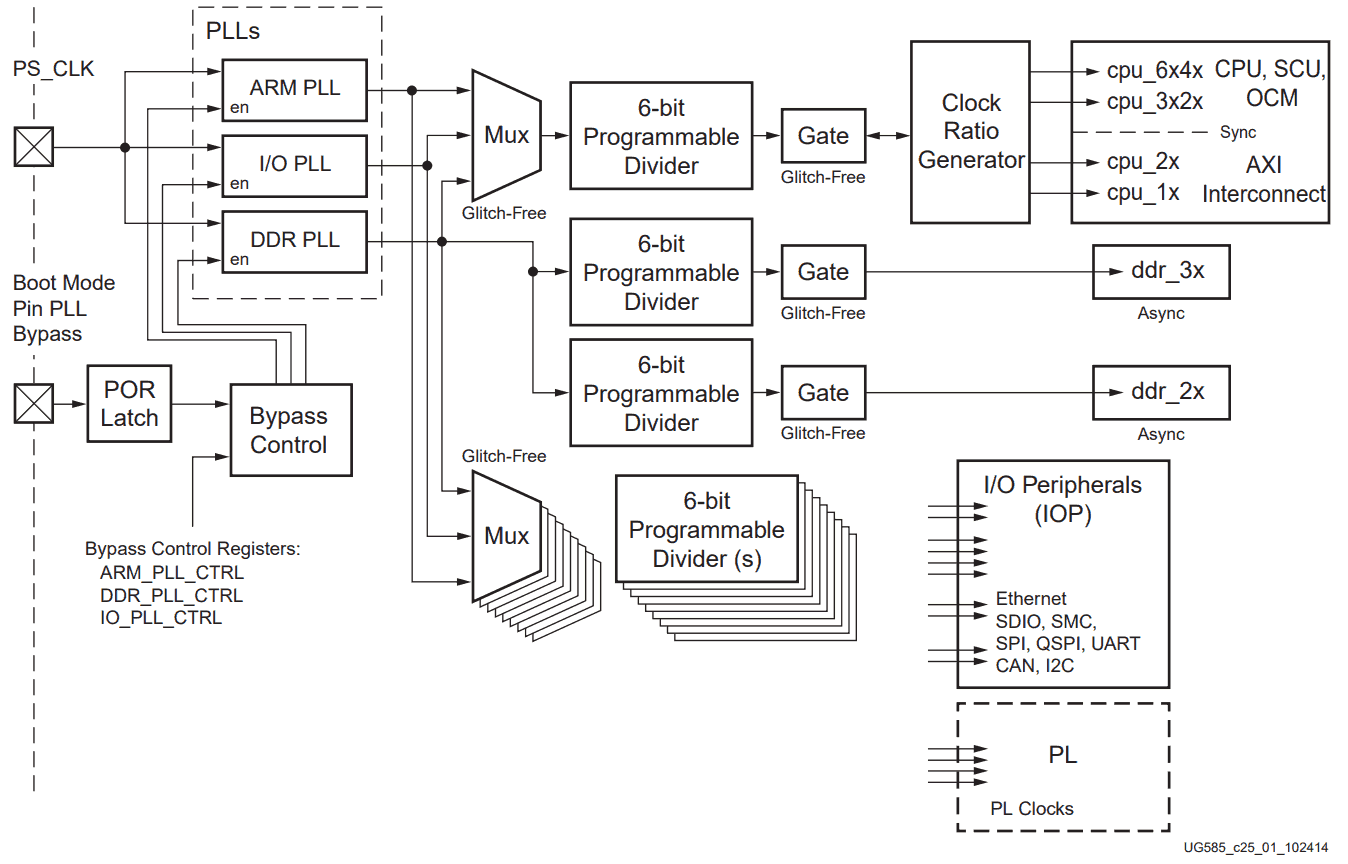

![1: Block diagram of the Zynq-7000 SoC. Adapted from Figure 1.2 in [8]. | Download Scientific Diagram 1: Block diagram of the Zynq-7000 SoC. Adapted from Figure 1.2 in [8]. | Download Scientific Diagram](https://www.researchgate.net/publication/370105463/figure/fig1/AS:11431281150422006@1681889750436/Block-diagram-of-the-Zynq-7000-SoC-Adapted-from-Figure-12-in-8.png)

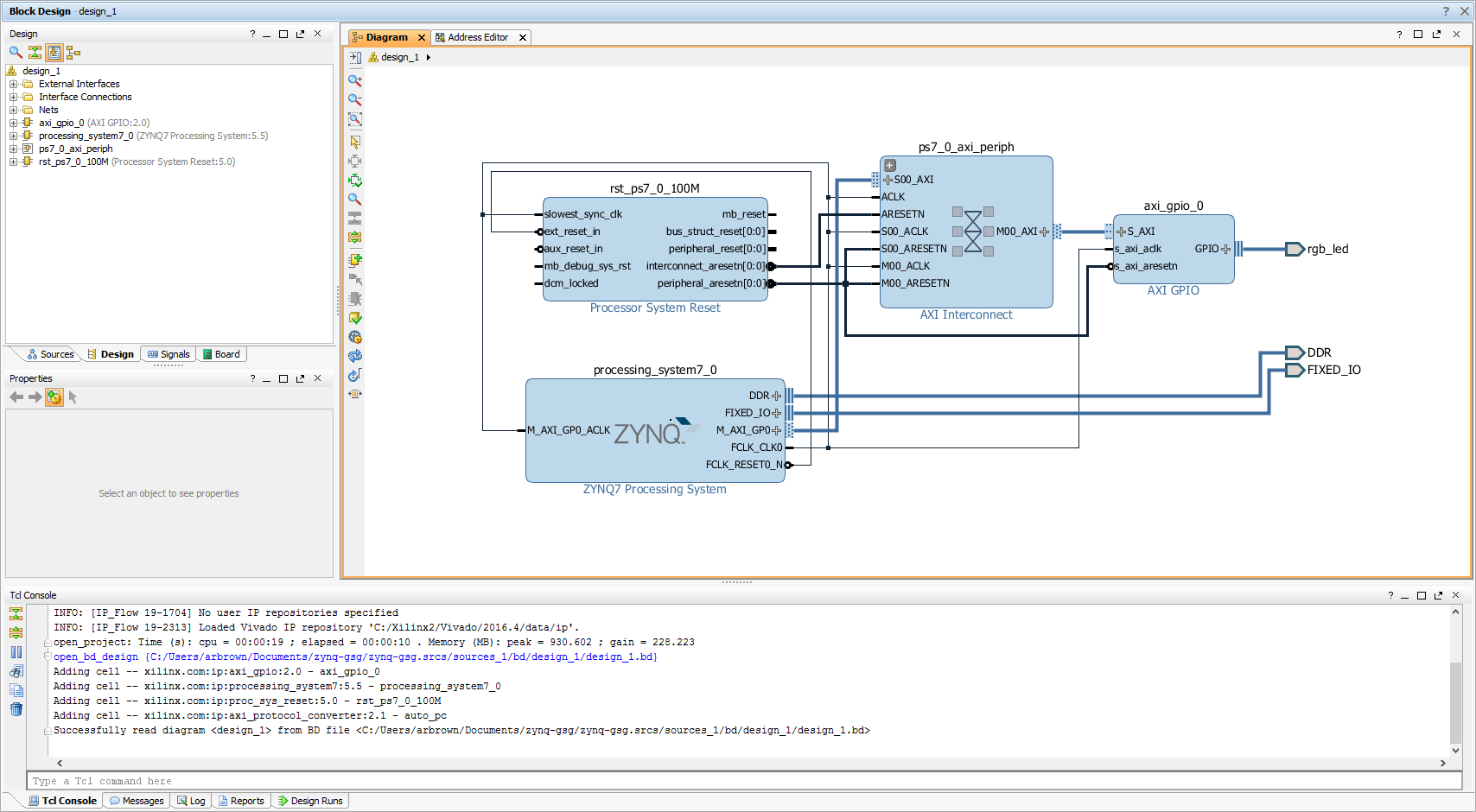

1: Block diagram of the Zynq-7000 SoC. Adapted from Figure 1.2 in [8]. | Download Scientific Diagram

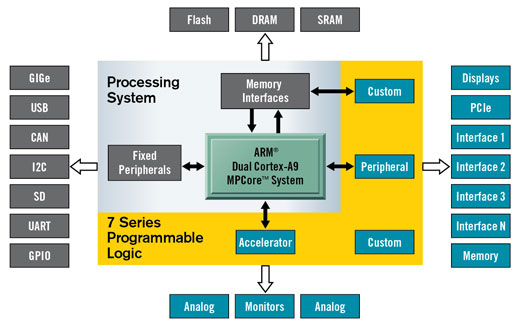

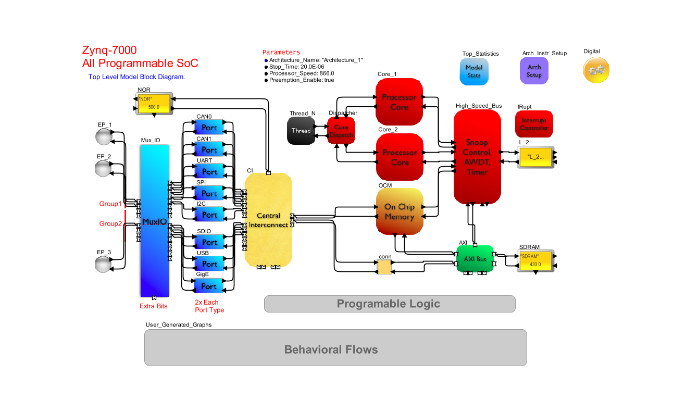

Xilinx zynq-7000 MYC-C7Z015 CPU Module Function Block Diagram | Design solutions, Linux, Development board

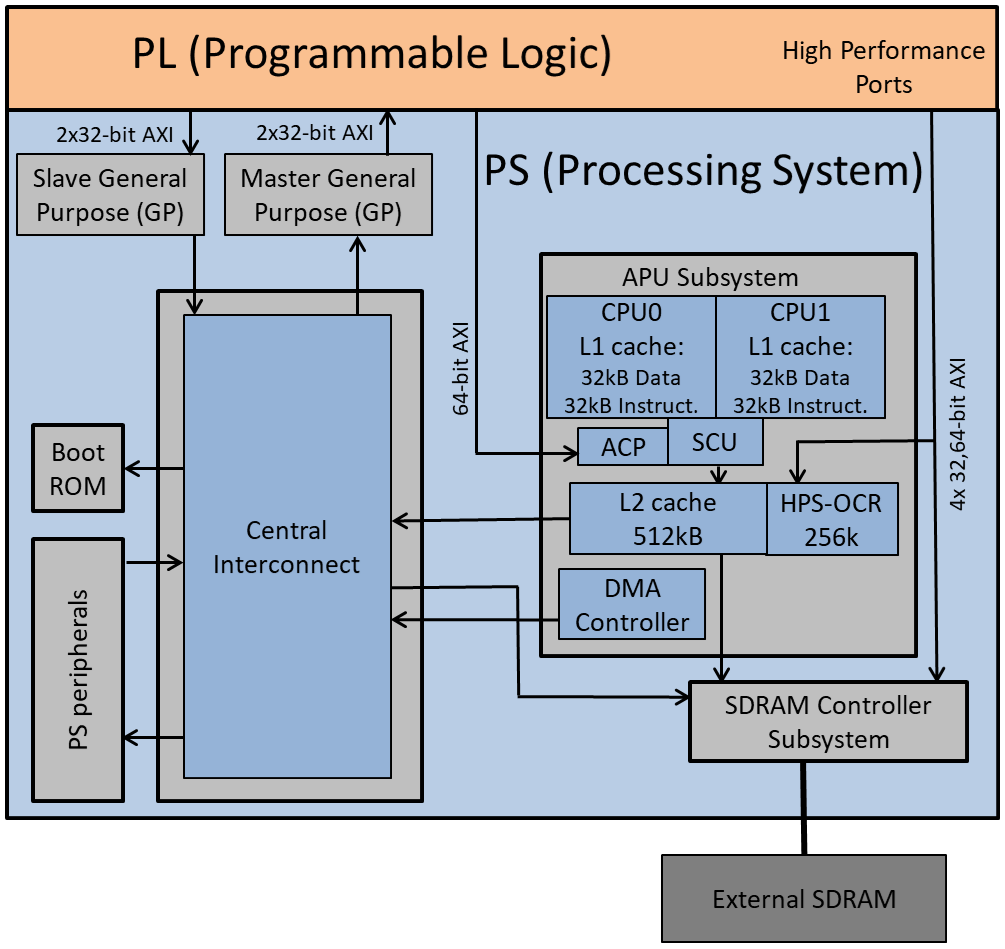

Functional diagram of the DAQ system implemented on the Zynq 7000 with... | Download Scientific Diagram

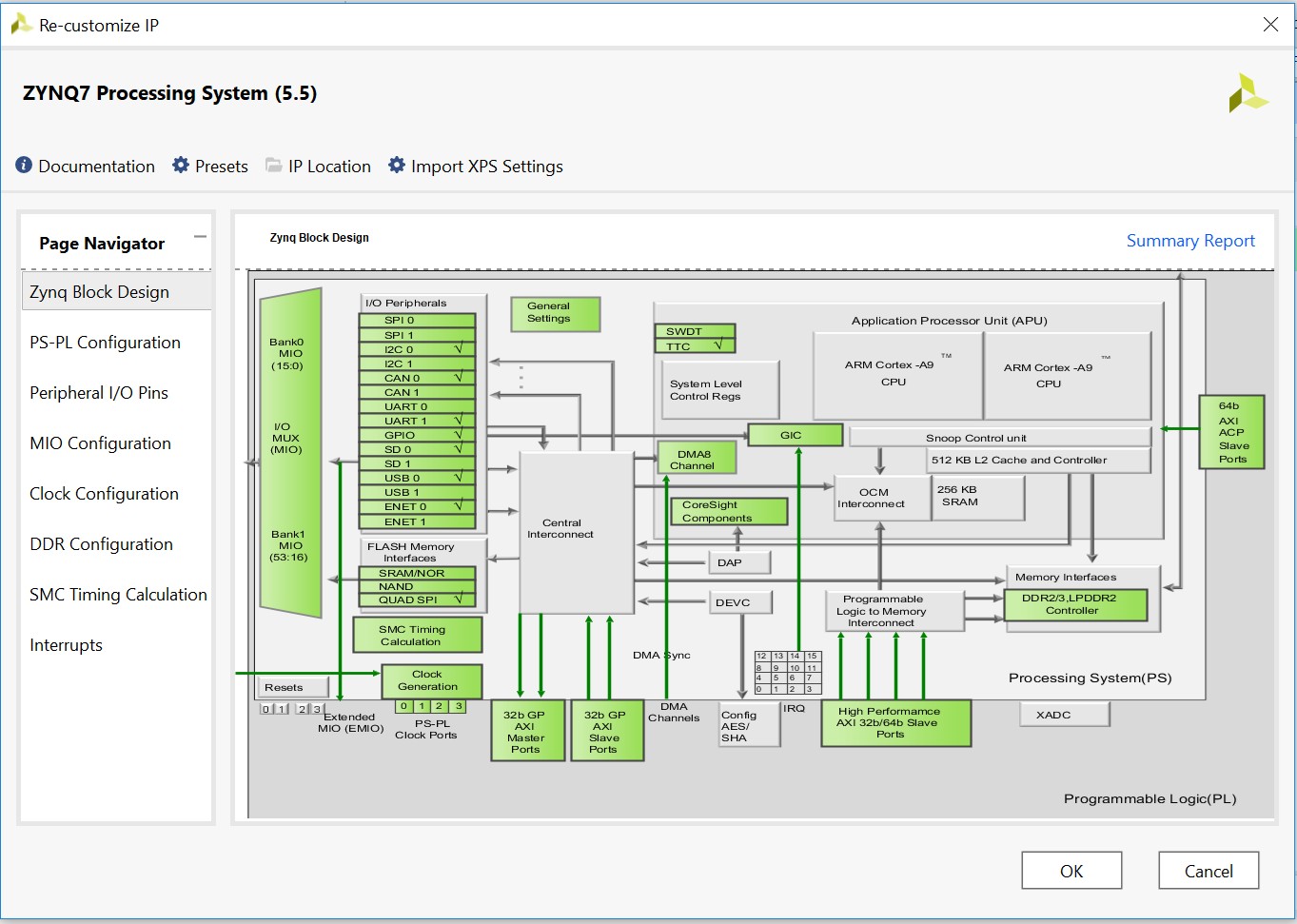

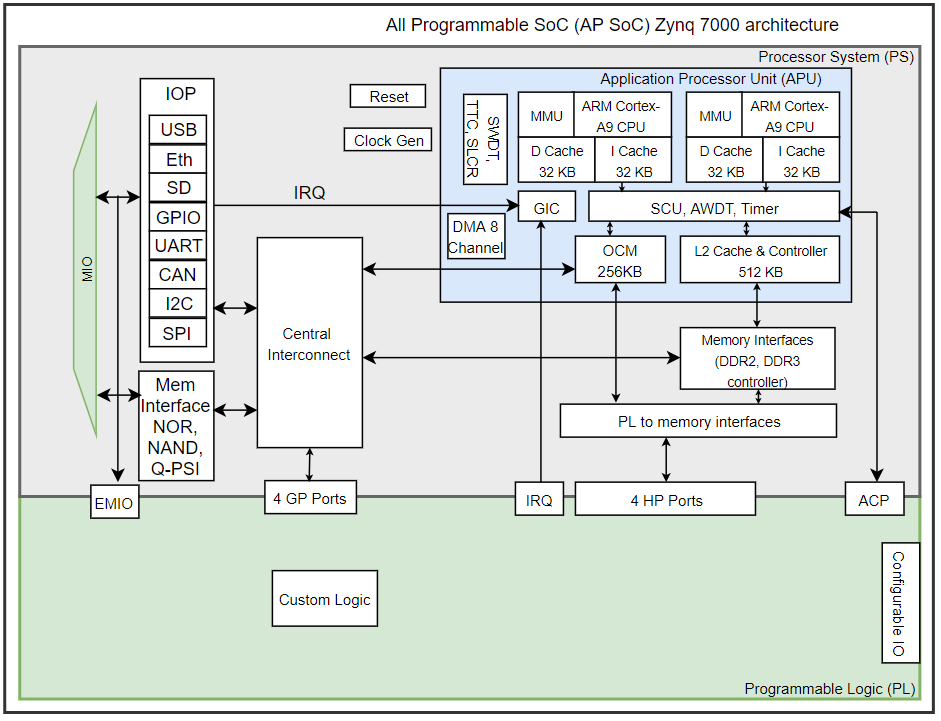

![Block diagram of the Zynq-7000 AP SoC [3]. | Download Scientific Diagram Block diagram of the Zynq-7000 AP SoC [3]. | Download Scientific Diagram](https://www.researchgate.net/profile/Marcilei-Guazzelli/publication/292103042/figure/fig1/AS:325031579144193@1454504975016/Block-diagram-of-the-Zynq-7000-AP-SoC-3_Q320.jpg)